几款不同的CPU一些数据–备查

背景

方便大家对不同的CPU混个脸熟,有个整体概念。本来发布在知识星球,但是知识星球上格式看起来太影响阅读效率了,所以特意拿出来发到博客上

简单查看CPU我一般用 lscpu(默认自带) 命令,或者用复杂点的工具:hwloc 工具安装:

|

|

安装后生成结构图片命令:

|

|

生成字符结构,不要图片:

|

|

后面展示的都算是整体机构,所以还会附带有内存怎么接(一个多少条,每条多大,一个Numa node插了几个物理内存条),这些我博客上都有,就不展开了。一般都是对称的(每个node、socket对称,不对称肯定发挥不出来好性能)

intel E5 2682

大概是Intel 2012年的主流服务器CPU

|

|

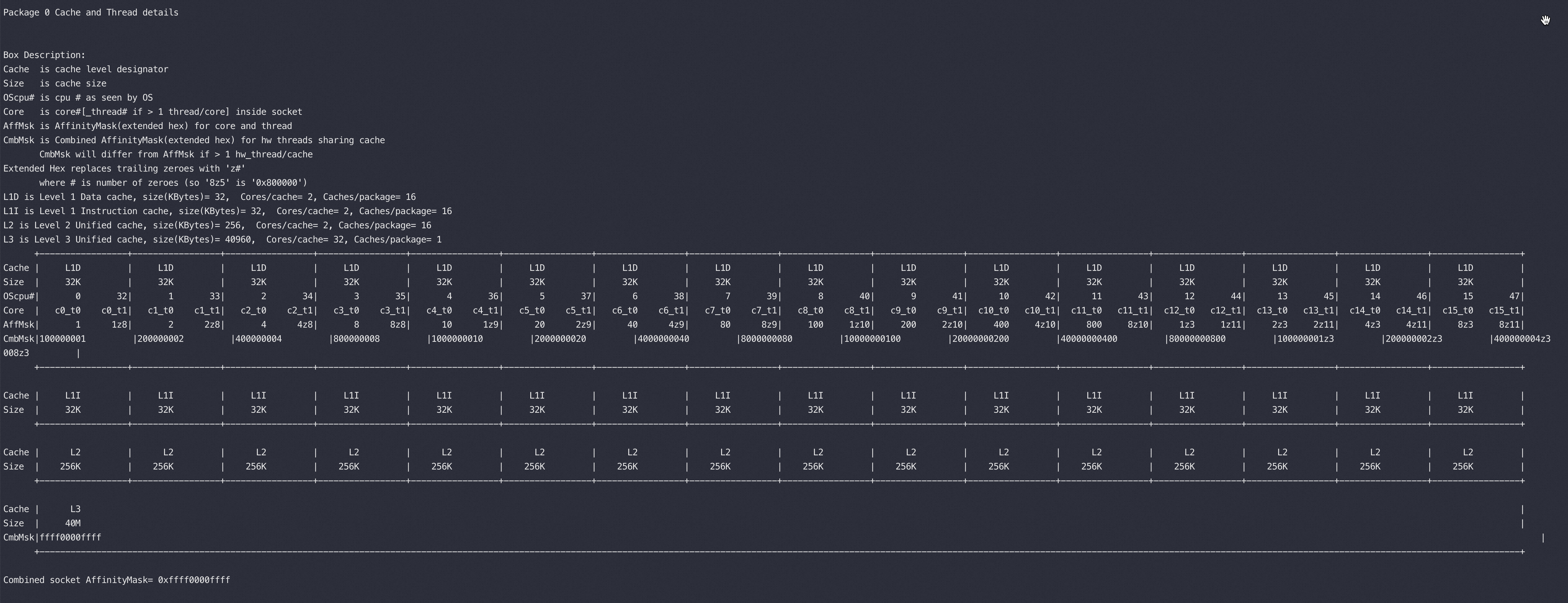

intel 还有一个自带的工具:cpuid-topo 可以看结构,以下是其中一个Socket的展示

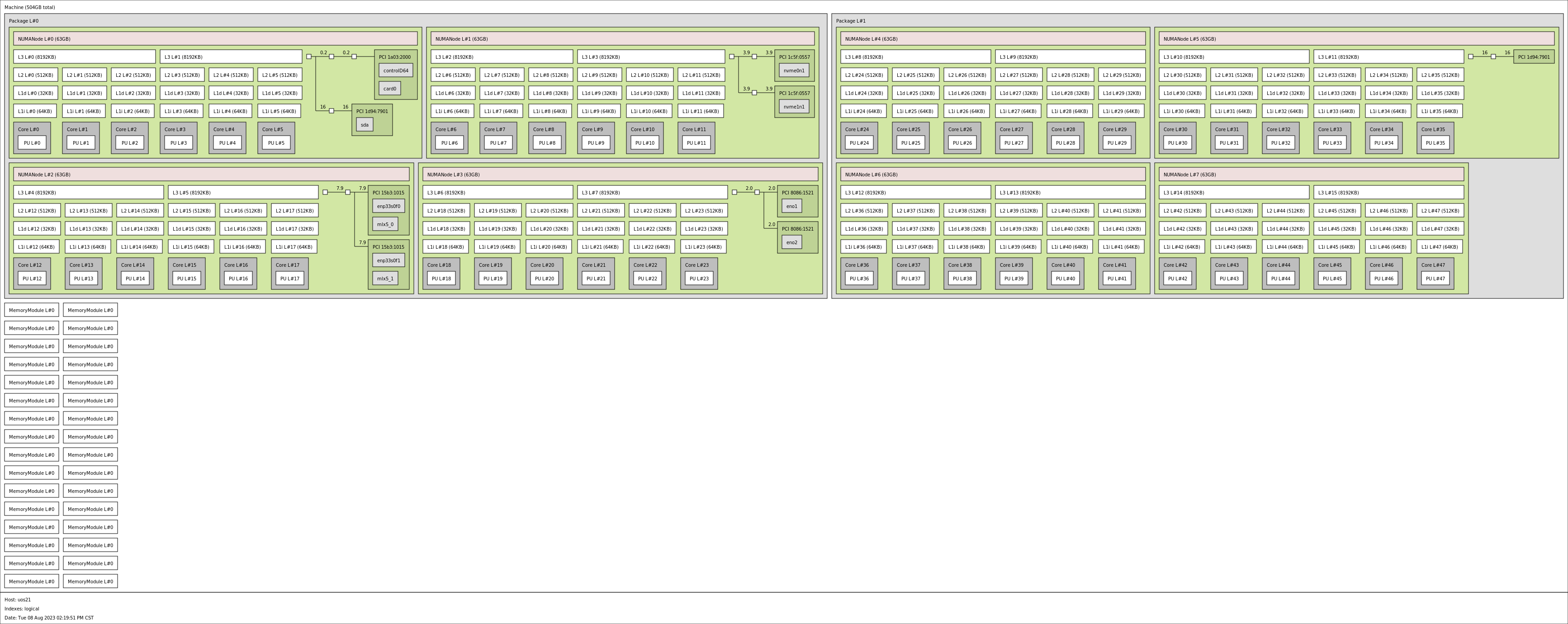

海光

购买的AMD版权设计等搞出来国产的 x86 架构

|

|

L1、L2太大了,好吓人,这么大不符合逻辑(太贵,没必要)

|

|

index0/index1 分别代表啥?

海光为啥搞了8个Node,请看:https://plantegg.github.io/2021/03/08/%E6%B5%B7%E5%85%89CPU/

图片可以看高清大图

对应的字符结构

|

|

以上是海光的7260,还有一个CPU是海光 7280:

|

|

作业:7260和7280的区别是?为什么搞了这两个差异很小的CPU?

|

|

还记得7260是3个物理核共享一个8M的L3吧,计算机的世界大多是1、2、4、8,看到3我就觉得有些别扭。评论区告诉我为什么会搞出3个核这样一个奇葩设计?(星球图解专栏里有答案)

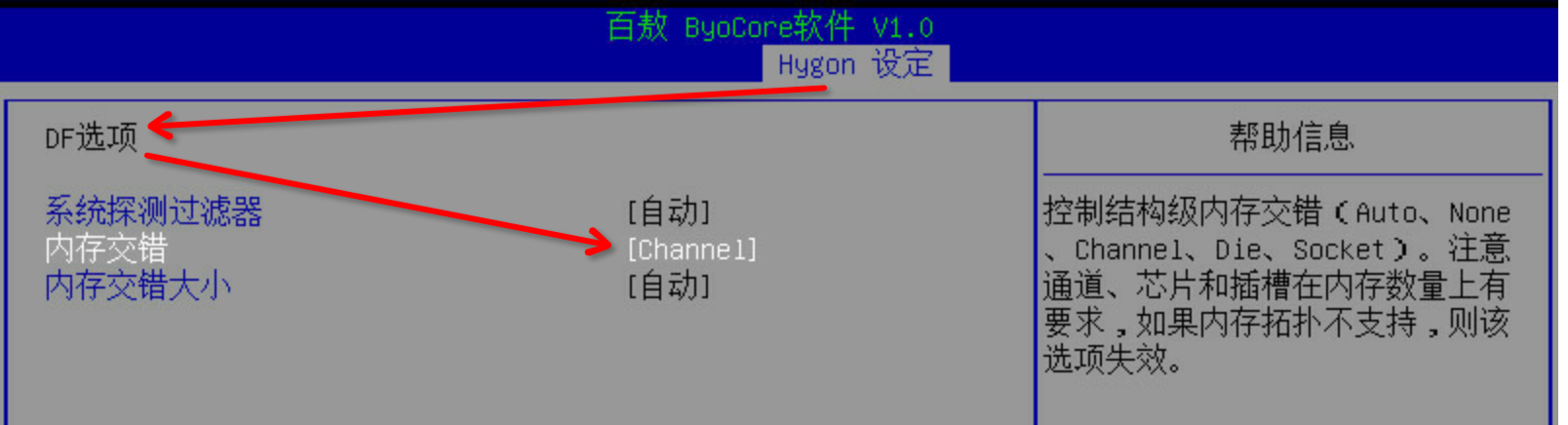

AMD 7T83

整机256核,一路128超线程,单CPU 64个物理核,很猛了

|

|

这台机器改下BIOS设置

白色Channel 那里可以选择Auto/Die/Channel/Socket, 选择Socket后得到如下Node 结构:

|

|

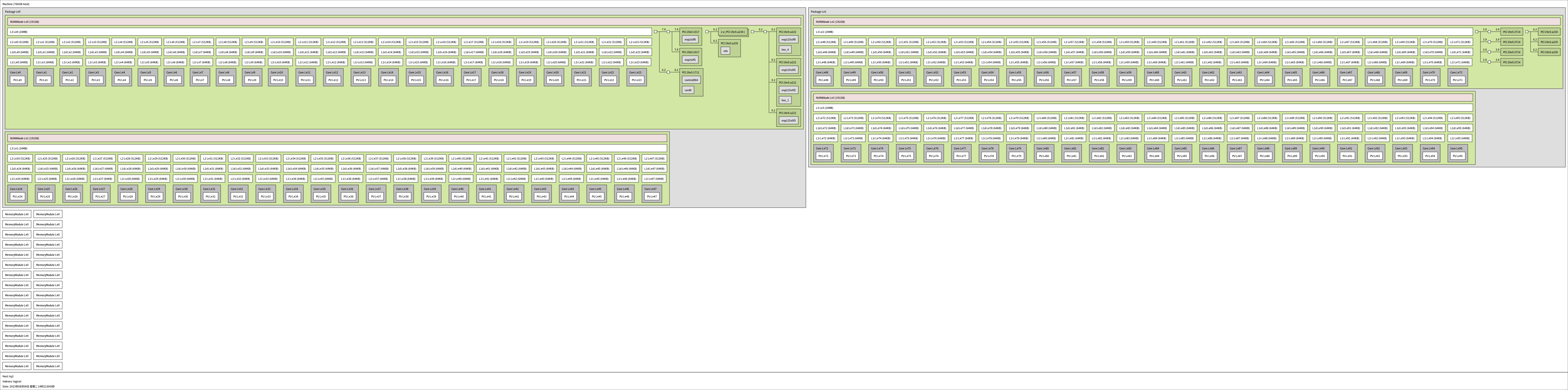

鲲鹏 920

鲲鹏是ARM架构,一般都没有超线程,因为指令简单流水线较流畅,搞超线程收益不大

|

|

图形化查看(打开大图,和前面的intel 对着看)

思考:看如上鲲鹏机器的结构你应该知道网卡、硬盘怎么插放的了吧,然后想就近搞点优化也是可以的

飞腾2500

飞腾的解读留给大家当作业

|

|

飞腾的核有点多,我省略了一些

|

|

不知名的一款CPU

当练习看看,随便看看

|

|

总结

希望通过具体又不同的CPU案例展示,让你对CPU的结构有一些整体认识

请问:Hygon C86 7260 这块CPU每个Die的L2、L3分别是多大?

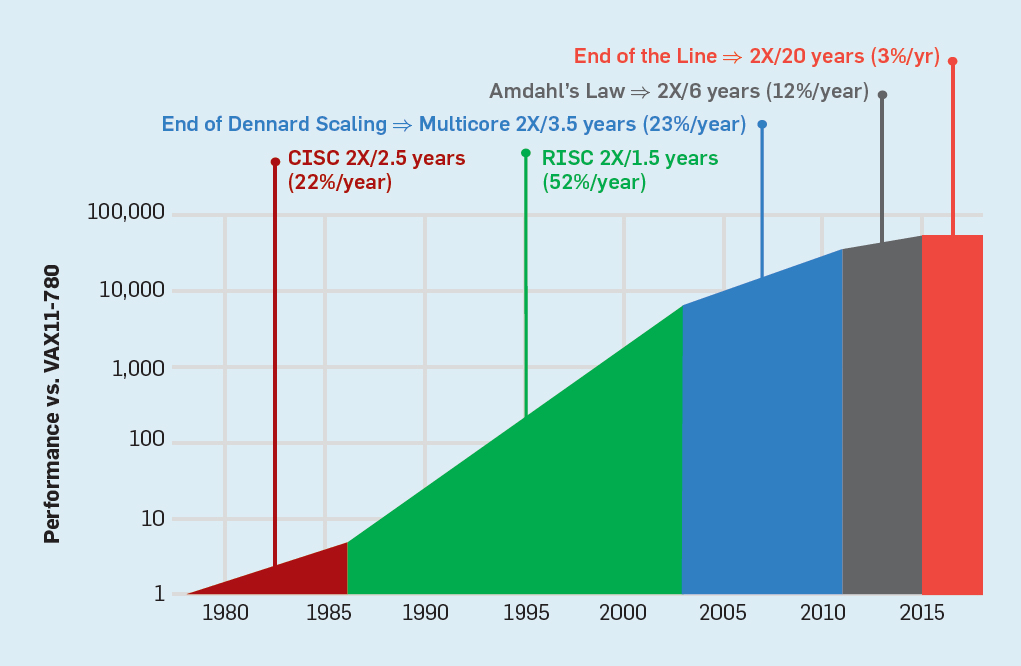

请思考,最近10年CPU的性能没啥大的进不了(如下图红色部分,每年3%),但是这么多年工艺还在进步,集成的晶体管数量

//这张图每一本计算机体系结构的教材都有引用(没有的话这教材可以扔了),你知道我博客里哪篇文章放了这图吗?从这个图你还能解析出来哪些东西?